출처 : https://www.youtube.com/watch?v=mTFYeZwPj0s&list=PLBrGAFAIyf5rby7QylRc6JxU5lzQ9c4tN&index=28

Virtual Storage Methods

- Paging system

이번 장에서는 실제로 운영체제들이 사용하는 virtual memory system 그 중에서 Paging system을 알아본다.

Paging system

- 프로그램을 같은 크기의 블록으로 분할 (Pages : 나누어진 블록)

- Terminologies

- Page

- 프로그램의 분할된 block

- Page frame : 페이지를 넣는 틀

- 메모리의 분할 영역

- Page와 같은 크기로 분할

- Page

Swap device에 있는 블록들이 하나의 프로세스가 되는 것이다. 그리고 이 프로세스를 같은 크기로 나눈 것이 페이지이다.

그리고 나누어진 페이지들 중에서 실제로 사용할 페이지들이 메모리에 올라가게 된다. 이때, 페이지들은 Non-continuous 하게 메모리에 적재되게 된다.

그리고 Non-continuous allocation을 page 크기로 나눈 것을 Paging System 이라고 한다.

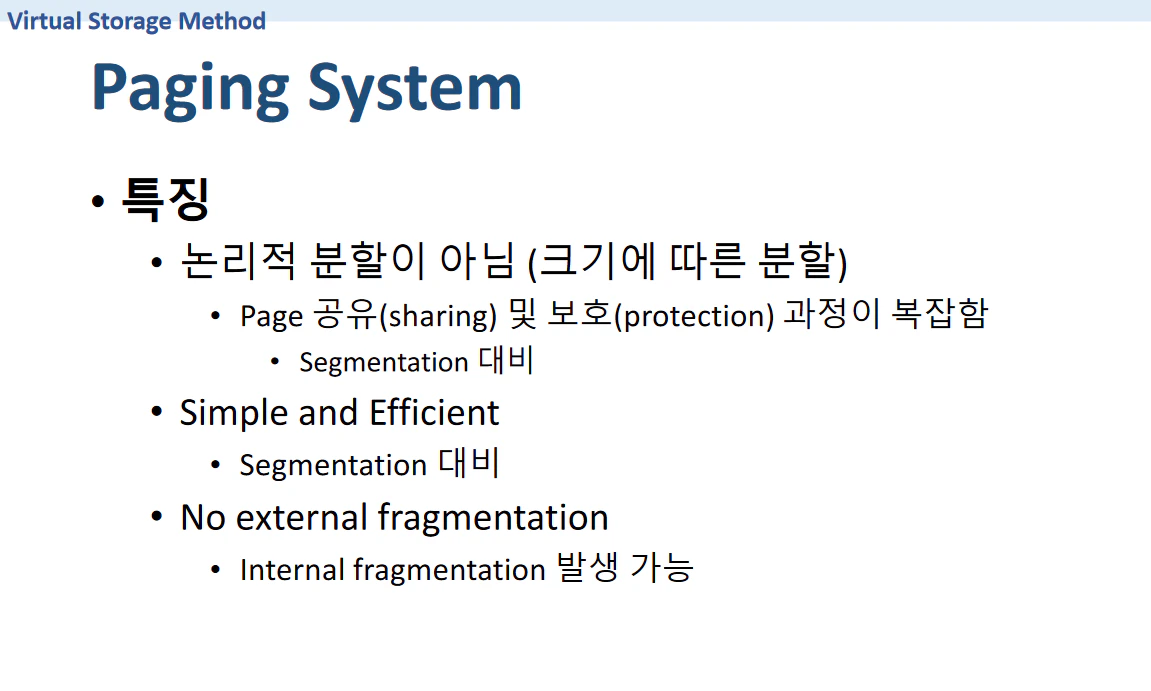

- 특징

- 논리적 분할이 아님 (크기에 따른 분할. 그냥 일정한 크기로 분할한 것임)

- Page 공유 (sharing) 및 보호 (Protection) 과정이 복잡함

- Segmentation 대비

- Page 공유 (sharing) 및 보호 (Protection) 과정이 복잡함

- Simple and Efficient

- 같은 크기로 분할한 것이기 때문에 간단하고, 간단하기 때문에 관리가 쉽다 = 효율적이다.

- Segmentation 대비

- No external fragmentation

- 프로세스와 메모리가 동일한 크기로 분할되기 때문에 메모리 공간이 충분한데 프로세스(이 경우에는 page)를 적재하지 못 하는 external fragmentation은 발생하지 않는다.

- Internal fragmentation 발생 가능

- 우리가 메모리를 동일한 크기로 나누다보니 맨 마지막에는 짜투리가 남을 수 있다. 이때, 이 짜투리 공간은 page frame보다 작기 때문에 프로세스를 담지 못하고 낭비되게 된다.

- 논리적 분할이 아님 (크기에 따른 분할. 그냥 일정한 크기로 분할한 것임)

제어판 -> 시스템 -> 고급 시스템 정보 -> 고급 -> 성능 옵션 -> 고급 을 들어가면 가상 메모리 부분에 페이징 파일이 명시적으로 보인다. 즉, windows는 실제로 페이징 시스템을 사용한다.

이 가상 메모리를 들어가면 우리가 swap device를 어떤 드라이브로 설정할 것인지, 크기는 어떻게 설정할 것인지를 제어할 수 있다.

Address Mapping

block mapping과 거의 유사하다.

- Virtual address : v = (p, d). (block mapping에서는 v = (b, d))

- p : page number

- d : displacement(offset)

- Address mapping

- PMT(Page Map Table)을 사용. (block mapping에서는 BMT(Blocdk Map Table)을 사용)

- Address mapping mechanism

- Direct mapping (직접 사상). (block mapping과 거의 유사)

- Associative mapping (연관 사상)

- TLB (Translation Look-aside Buffer)

- Hybrid direct / associative mapping

- Page Map Table (PMT)

- Page number : 페이지 넘버

- residence bit : 메모리에 적재되어 있는가?

- Page frame number : page frame 번호 = 메모리 어디에 적재되어있는가?

- Secondary storage address : 프로세스(=페이지들)은 모두 swap device에 저장되어있다. 이때, swap device의 어디에 저장되어있는가?

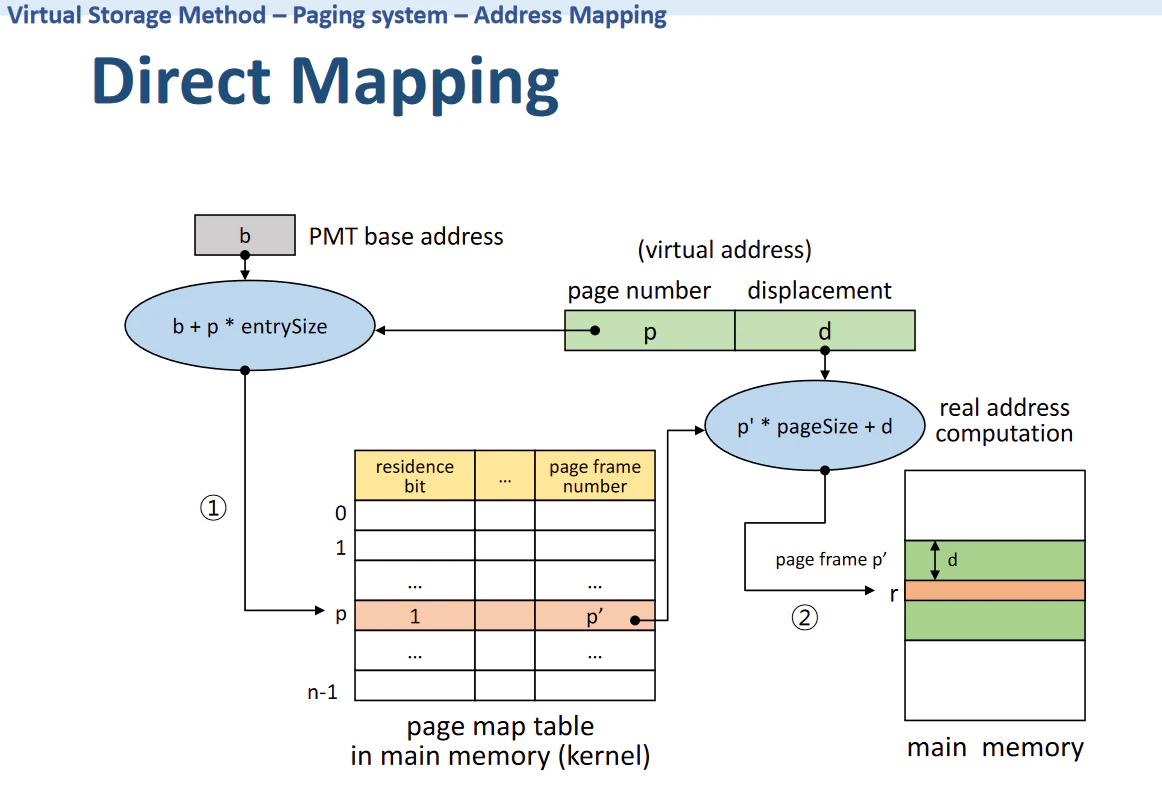

- Direct mapping

- Block mapping 방법과 유사

- 가정

- PMT를 커널 안에 저장

- PMT entry size (PMT 한 줄의 사이즈) = entrySize

- Page size (프로세스를 나눈 페이지의 크기) = pageSize

Direct Mapping

Virtual address v = (p, d)로 이루어진다.

커널 안에 있는 PMT에서 해당 page number p를 보고 residence bit를 확인한다(=메모리에 적재되어있는지를 확인한다).

이때, PMT가 저장되어있는 기본 주소 b를 알고있다고 가정한다. 그러면 기본 주소 b + (p*entrySize = p*PMT의 줄 수)를 계산하면 우리가 원하는 entry를 찾아갈 수 있다.

만약 residence bit가 1이라면 (= 해당 페이지가 메모리에 적재되어있다면) 몇 번째 page frame에 있는지를 나타내는 page frame number p'이 주어진다.

[p' * pageSize(=하나의 페이지 크기) = 실제 메모리 시작 주소] + d(시작 위치로부터 얼마나 떨어져있는가)를 계산하면 우리가 원하는 real address를 찾아갈 수 있다.

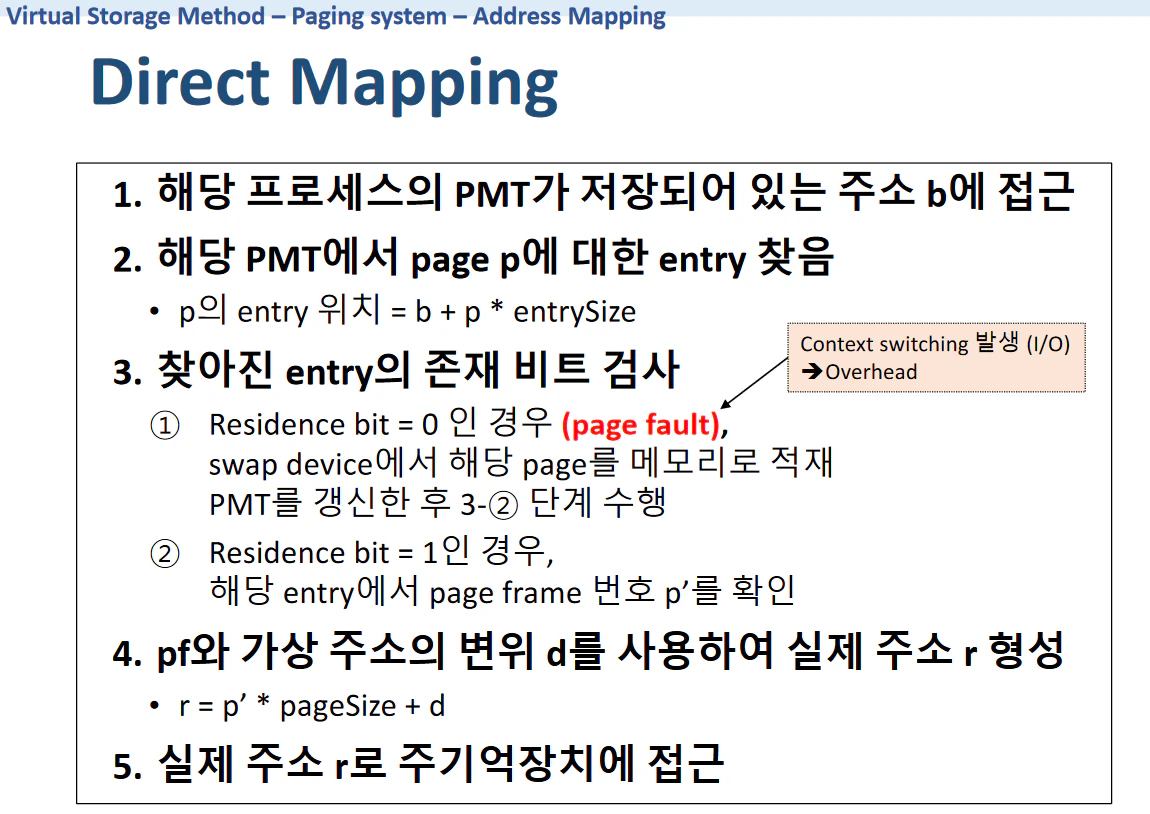

Direct Mapping 과정을 정리하면 다음과 같다.

- 해당 프로세스의 PMT가 저장되어 있는 주소 b에 접근

- 해당 PMT에서 page p에 대한 entry를 찾음

- p의 entry 위치 = b + p * entrySize

- 찾아진 entry의 존재 비트 검사

- Residence bit = 0인 경우 (page fault라고 부름. 페이지를 읽는데 실패했다는 뜻), swap device에서 해당 page를 메모리로 적재한 다음 PMT를 갱신한 후 3-2 단계를 수행

- Residence bit = 1인 경우, 해당 entry에서 page frame 번호 p'을 확인

- Page frame과 가상 주소의 변위 d를 사용하여 실제 주소 r 형성

- r = p' * pageSize + d

- 실제 주소 r로 주 기억장치에 접근

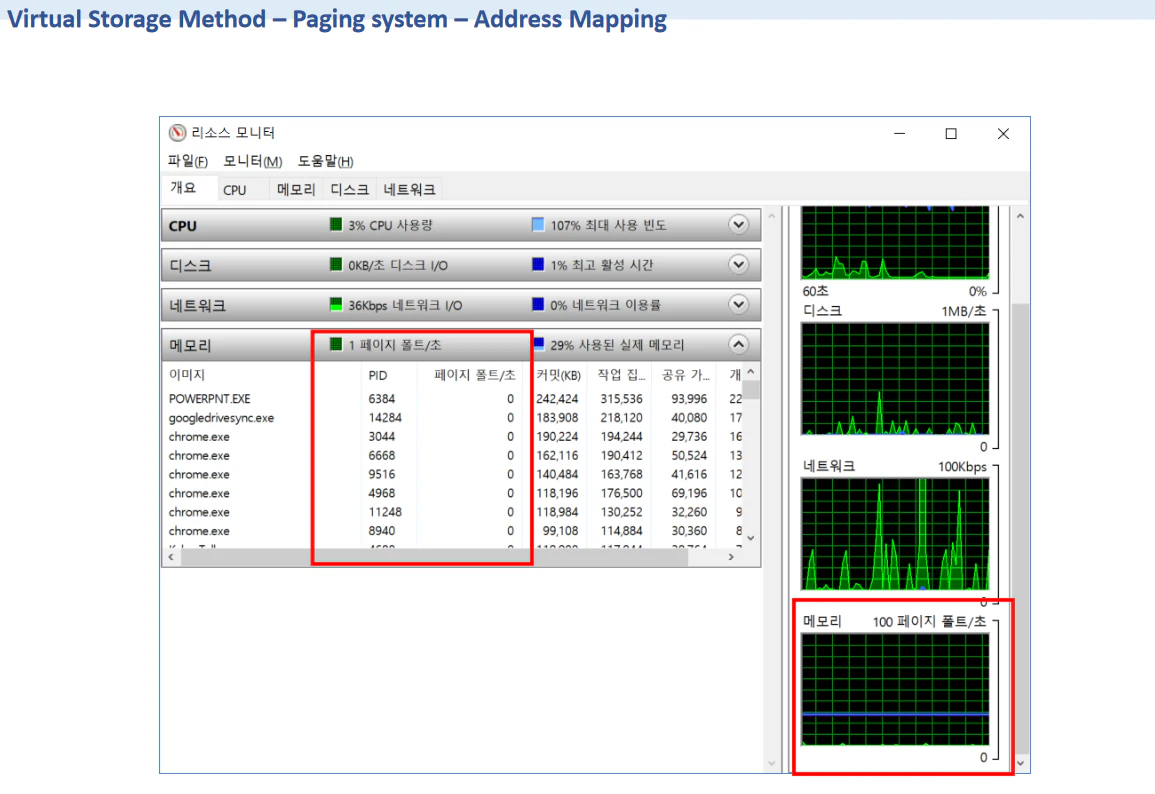

작업 관리자 -> 성능 -> 리소스 모니터를 들어가보면 자원의 상세 정보를 볼 수 있다.

- 문제점

- 메모리 접근 횟수가 2배

- 우리가 원하는 메모리 영역 r에 접근하기 위해서 main memory에 있는 커널에서 PMT를 보는데 1번 + 그 다음 r에 접근하는데 1번 = 2번 접근한다.

- 성능 저하 (Performance degradation)

- PMT를 위한 메모리 공간 필요 = 메모리 공간의 overhead

- 메모리 접근 횟수가 2배

- 해결 방안

- Associative mapping (TLB)

- PMT를 위한 전용 기억장치(공간) 사용

- Dedicated register or cache memory

- Hierarchical paging

- Hashed page table

- Inverted page table

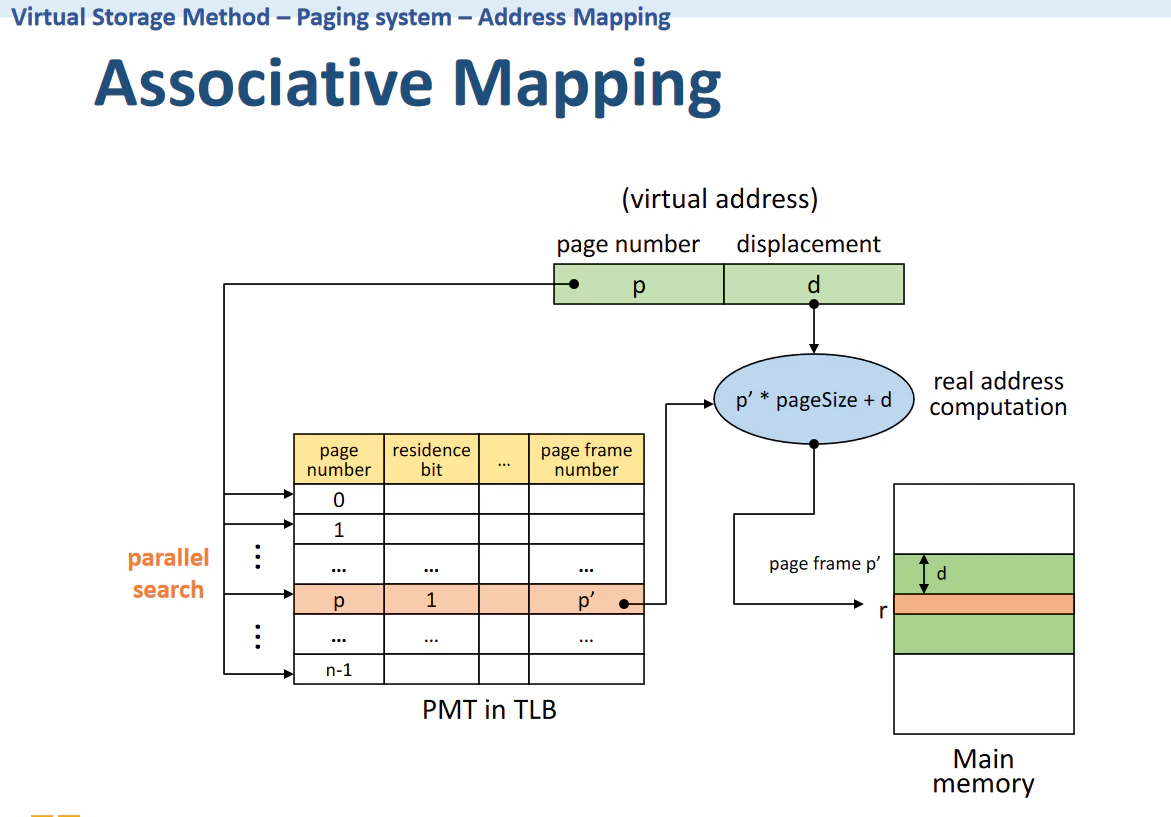

Associative Mapping

- TLB(Translation Look-aside Buffer)에 PMT 적재

- Associative high-speed memory = PMT를 탐색하기 위한 전용 HW

- PMT를 병렬 탐색

- Low overhead, high speed

- Expensive hardware (비싸다 = 작다)

- 큰 PMT를 다루기가 어려움

PMT를 TLB에 넣어놓는다. 이때 virtual address의 p가 주어지면 PMT에서 병렬로 동시에 page number를 탐색을 해서, page frame number를 한 번에 출력한다.

하드웨어가 해결해주므로 굉장히 빠르고, 메모리가 아닌 TLB에서 해결하기 때문에 메모리 접근 횟수가 줄어들고 그로인해 overhead가 줄어들게 된다.

즉, address mapping을 굉장히 빠르게 할 수 있다.

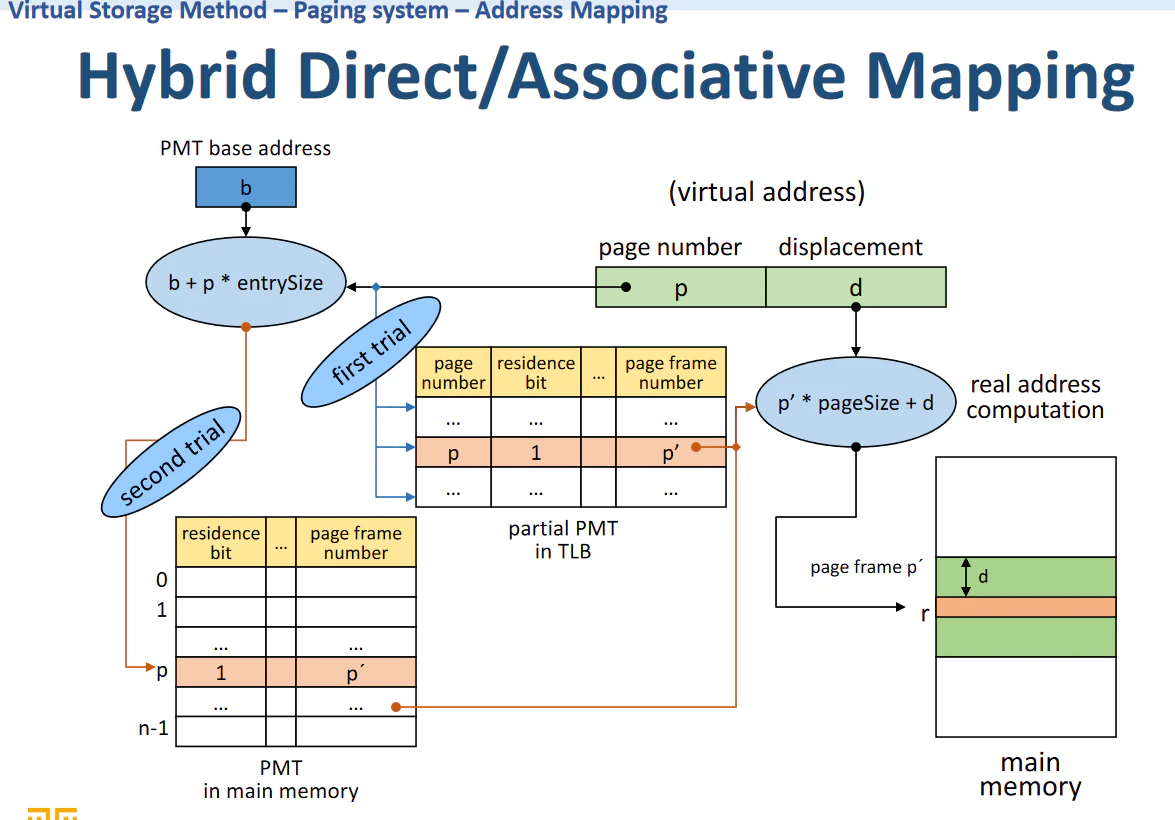

Hybrid Direct / Associative Mapping

- 두 기법을 혼합하여 사용

- HW(TLB) 비용은 줄이고, Associative mapping의 장점 활용

- 작은 크기의 TLB 사용

- PMT : 메모리(커널 공간)에 저장

- TLB : PMT 중 일부 entry들을 적재

- 최근에 사용된 page들에 대한 entry 저장

- Locality (지역성) 활용

- 프로그램의 수행과정에서 한 번 접근한 영역을 다시 접근(temporal locality) 또는 인접 영역을 다시 접근(spatial locality)할 가능성이 높음

- 프로세스의 PMT가 TLB에 적재되어 있는지 확인

- TLB에 적재되어 있는 경우, Associative mapping을 사용

- Residence bit를 검사하고, page frame number 확인

- TLB에 적재되어 있지 않은 경우

- Direct mapping으로 page frame number 확인

- 해당 PMT entry를 TLB에 적재함

- TLB에 적재되어 있는 경우, Associative mapping을 사용

즉, TLB에 해당 page number가 있으면 바로 p' * pageSize + d를 계산해서 real address r에 접근한다.

만약 TLB에 해당 page number가 없으면 direct mapping을 써서 real address r에 접근한 다음, 해당 정보를 TLB에 저장한다.

'Study > 운영체제' 카테고리의 다른 글

| 운영체제 9. 가상 메모리 (4) - Segmentation System (1) | 2023.12.01 |

|---|---|

| 운영체제 9. 가상 메모리 (3) - paging system (2) (0) | 2023.11.30 |

| 운영체제 9. 가상 메모리 (1) - Non-continuous allocation (2) | 2023.11.27 |

| 운영체제 8. 메모리(주 기억장치) 관리 (3) - Variable Partition Multi-programming (2) | 2023.11.27 |

| 운영체제 8. 메모리(주 기억장치) 관리 (2)- Fixed Partition Multiprogramming (0) | 2023.11.25 |